# AN IEEE-1394 BASED OUTLET FOR HOME AUTOMATION AND HEALTH CARE NETWORKS

# S. Martel, I. Hunter

BioInstrumentation Laboratory, Massachusetts Institute of Technology, Cambridge, MA, USA

Abstract-This paper describes a new outlet intended for a future home and/or office network based on the IEEE-1394 serial bus. The new outlet has been built and tested. Several units can be distributed throughout the home to provide high-speed interconnection among various systems designed for home automation and/or health care applications.

Keywords - Network, home automation, health care, asynchronous, isochronous, FireWire, IEEE-1394, outlet.

#### I. INTRODUCTION

The IEEE-1394 serial bus also known as "FireWire" is a versatile, high-speed, and low-cost method of interconnecting a variety of personal computer (PC) peripherals and consumer electronics devices. The high speed FireWire and the low speed Universal Serial Bus (USB) will be in a near future the only interconnections available on PCs. Hence, by choosing the high-bandwidth IEEE-1394 serial bus, a home automation and/or health care network could be connected directly to any PCs without additional adapters. The integration of IEEE-1394 drivers as part the PC operating systems will ease the implementation and compatibility issue of the proposed home automation network with unlimited access to information and services across the nation and around the world.

If the IEEE-1394 succeeds in the home automation and health care areas, then one of the fundamental requirements will be to provide an easy and low cost method to interconnect together these IEEE-1394 compatible devices throughout the home. A proposed solution is to have multiple special wall outlets providing the link between various types of devices and the IEEE-1394 network. A first implementation of such outlet is described briefly.

### II. OVERVIEW OF THE IEEE-1394

FireWire provides a direct digital link among up to 63 devices. The number of accessible devices within the same house can be expanded to 65535 if deemed necessary. The present implementation of IEEE-1394 can deliver 100 Mbps, 200 Mbps, or 400 Mbps of data payload and control signals. Future versions that support data rates exceeding 400 Mbps are under development. An important feature of FireWire is its isochronous data transmission mode that lets even the 100 Mbps implementation to support two simultaneous channels of full-motion (30-frames-per-second) video and CD-grade stereo audio. This is ideal for many applications including home security and entertainment. The actual maximum distance between two successive IEEE-1394 outlets is 4.5 meters. An advantage of this technology is its low cost. The IEEE-1394 technology uses a flexible, six-conductor cable and connectors derived from Nintendo's Gameboy to interconnect devices. Use of FireWire for consumer electronic gear, such as camcorders and VCRs, will provide the high-volume market needed to achieve low-cost implementation. Furthermore, FireWire extends Plug and Play (PnP) features far beyond the confines of the PC. When you add or disconnect a device within the house or office, the network will automatically detect it and reconfigure itself without user's intervention.

### III. IEEE-1394 OUTLET

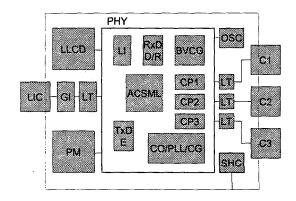

The proposed outlet implements the network's physical (PHY) layer. The three primary functions of the PHY layer are the transmission and reception of data bits, arbitration, and provision for the electrical as well as the mechanical interface. The block diagram of the outlet is shown in Fig. 1.

The new outlet, represented in Fig. 1, has three IEEE-1394 connectors (C1, C2, and C3) and one optional link interface connector (LIC). Each connector has an associated line termination (LT) block for the signals. The LIC has also an optional galvanic isolation (GI) block to prevent excessive ground loop noises when several units are connected through the serial bus. The signals from C1, C2 and C3 are connected to respective cable ports (CP1, CP2, and CP3) to be handled by the received data decoder/re-timer (RxDD/R) and the transmitted data encoder (TxDE). If a link layer controller (LLC) located on a device connected to the LIC is detected through the LLC detector (LLCD), data would be exchanged through the link interface (LI) block. A 24.5760 MHz parallel resonant fundamental mode crystal (OSC) acts as the internal clocking source for the outlet. The crystal oscillator/phaselock loop/clock generator (CO/PLL/CG) block derives from the OSC all additional synchronization signals required for the unit's proper operation. Bias voltage and current for the line termination blocks, are provided by the bias voltage and current generator (BVCG).

Fig. 1. Block diagram of the outlet

The power management (PM) block is responsible for voltage regulations and conversions for the unregulated IEEE-1394 cable power lines as well as providing filtered ground interconnections. A shield connection (SCH) block has the required circuitry to connect the IEEE-1394 cable's shield to the outlet's shielded box. The central operational control of the outlet at the network's physical layer is achieved with an "arbitration and control state machine logic" (ACSML) block. More details on the outlet's functionality can be found in [1] and [2].

### IV. IMPLEMENTATION

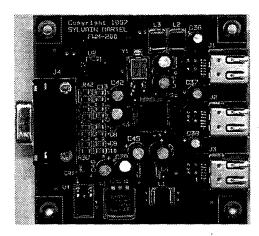

The present implementation was designed for research and a much simplified and lower cost unit better suited for the commercial market but with less flexibility can be derived easily from this model. By depopulating the unit, several versions can be implemented. The physical model can also be altered. One commercial alternative would be to use a vertical version of C1, C2, and C3, with two connectors on one side of the PCB and one connector on the opposite side. The unit could be mounted on any side depending if one or two ports (facing the internal wall) are used for networking, making the free port(s) available to the consumer. A photograph of the present outlet implementation is shown in Fig. 2. The size is  $76.2 \times 76.2 \text{ mm}$  (3.0 × 3.0 inches) with height of 15.25 mm (0.6 inch).

Fig. 2. Photograph of the outlet

The size of the outlet can be reduced further. For instance, by eliminating the optional link layer connection, the LIC, GI with corresponding LT, as well as the LLCD could be eliminated from the block diagram depicted in Fig. 1, reducing the size of the PCB significantly. Furthermore, the electrolytic capacitors could be replaced by capacitors with lower vertical dimension, reducing the overall height of the outlet down to approximately 10.5 mm (0.4 inch). The present unit as 4 plated mounting holes as shown in Fig. 2, which can be used for mounting the unit, attaching a shielded box and providing shielding connection between the outlet's shield and the IEEE-1394 cable shield through the SHC block.

The present unit is referred to as "FWM-200", which stands for FireWire Module running at 200 Mb/s (196.608 Mb/s). The unit could be easily upgraded to the "FWM-400" (393.216 Mb/s). The PHY block for the FWM-200 as depicted in Fig. 1 has been implemented with the TSB21LV03 triple-cable transceiver/arbiter [2] also shown in the middle of the outlet in Fig. 2. Also as depicted in Fig. 2, the crystal oscillator is next to the TSB21LV03 to minimize EMI. To minimize the effect of potential EMI and other switching noises such as cross-talk and ground bounces, the FWM-200 also has several ferrite beads with high impedance above DC distributed throughout the various grounds and power lines as well as ceramic capacitors and low ESR electrolytic capacitors. We designed the unit for worst case scenarios since no exact data of the anticipated noise level were available prior to the implementation. Based on our measurements, the unit could be further simplified by removing some of the beads and de-coupling capacitors and using other parts having smaller physical dimensions including the possibility of replacing the electrolytic by tantalum capacitors with potentially higher ESR.

The outlet does not need batteries or transformers since it is entirely powered by the IEEE-1394 cables. Part of the PM has two voltage regulators for +5 VDC output (78M05CDT) and +3.3 VDC output (LT1086CM-3.3). The 5 VDC output is protected against large voltage fluctuations by a SOT-23 5.6V zener diode. The unregulated 12 VDC of the IEEE-1394 cable is connected to the input of the 78M05. A tiny surfaceprinted jumper allows the input of the LT1086 to be connected directly to the unregulated 12 VDC or to the 5 VDC generated by the 78M05, which is possible considering the low drop out of the LT1086. The advantage of the last scheme is a reduction of the LT1086 power dissipation. This configuration allowed us more flexibility for experimentation and testing. Future versions of the outlet could be easily simplified with the use of only one voltage regulator. The PM block also includes a power-reset circuit to initialize the outlet's PHY layer properly after connecting the first IEEE-1394 cable on any of the three available connectors.

The LLCD block consists of resistors and an optocoupler (TIL191A) for isolation purpose. The LLCD can detect the presence of a LLC through a reserved connection on the LIC providing the link power status (LPS). Monitoring the LPS can be achieved by sensing the LLC power line or a pulsed signal between 200 kHz and 5.5 MHz present when the LLC is powered. To minimize EMI from high-frequency signals passing through inductive connections on the LIC, the LLC power line was selected as indicator for the FWM. Because of the DC component, this choice forced us to use an optocoupler instead of a transformer or a capacitor to provide isolation within the LLCD. The isolated output of the LLCD depending on the LPS then selects one of the two modes of operation of the PHY layer namely, LLC support or repeater mode [3].

The present unit implements the PHY-LLC interface isolation shown as GI in Fig. 1 (and next to the LIC in Fig. 2), using the capacitive-isolation circuitry as mentioned in Annex J of the IEEE 1394-1995 Standard. Several 1206-type jumpers can replace the isolation capacitors when isolation is not required. When doing so, a signal available on the FWM

is set internally to force the LI to disable the internal differentiating logic. Other types of implementations of the GI block as described in [4], for instance, can also be implemented in future versions.

The LT block for the LIC consists simply of several pull-up and pull-down resistors. The LT blocks associated with C1, C2, and C3 provides an external 112  $\Omega$  line-termination through pairs of 56  $\Omega$  resistors for each twisted-pair cable required for drivers operating in high-impedance current mode. The terminals are also coupled to ground through RC networks with values chosen to meet the IEEE-1394 draft specifications.

The PCB layout [5] was also performed to minimize transmission line effects, differential and common noise interference and antenna effects. As such, the etch length between the PHY and C1, C2, and C3 had to be minimized with a maximum distance depending upon the edge rates, the propagation time, and the matching impedance provided by the three LT blocks depicted in Fig. 1. With a simpler implementation without matching impedance, a rule of thumb from Texas Instruments specifies a maximum etch length "Le <  $(T_r \bullet (c / e_r^{1/2})) / 6"$  where  $T_r$  is the signal's rise time, c is the speed of light (2.997  $\times$  10<sup>8</sup> m/s), and e<sub>r</sub> is the PCB's dielectric constant. From the recent 1394a specifications limiting the minimum rise time to 0.5 ns and considering FR-4 maximum dielectric constant of 5.3, we have L<sub>e</sub> < 1.0 cm (0.4 inch). This specification has been met between PHY and C2 but could not be realized with C1 and C3. Practically, a maximum  $L_e = 2.0$  cm (0.8 inch) as in the present implementation would be more acceptable for the PCB layout, providing adequate distances between C1, C2, and C3. As such, the dielectric constant of the PCB needed to be at most  $e_r < (c T_r) / (6 L_e)^2 < 1.5625$  which is practically not possible to achieve at low cost. Even a minimum FR-4 dielectric constant of 4.0 only extends the maximum PCB trace by an extra 0.25 cm. Therefore, the three LT blocks were implemented to fulfill the 1394a specifications. Furthermore, the trace's length of twisted pair was matched as closed as possible and run in parallel. To do so, the LT blocks were implemented on the opposite side of the PCB at the expense of one via implemented per signal since C1, C2, and C3 were surface mounted. The clearance size around each via was increased slightly to minimize capacitance. Through hole connectors could have eliminated the need for via but were not selected because of significant inductance created by the pin-through holes.

The traces on the PHY-LLC interface were maintained as short as possible to minimize coupling and signal losses with equal length to minimize propagation delay mismatch. The present implementation uses a shielded D-type subminiature DB15 connector (LIC). The LPS, PHY-LLC transmission synchronization clock, and link request signals use one terminal each. The control signals uses two terminals, four terminals are reserved for half-duplex data transfers while the remainder pins are used for the unregulated PHY-12 VDC and the LLC isolated ground. All but the LPS, power and ground passes through the GI block. The ground is connected to the PM block through 1  $M\Omega \parallel 0.1~\mu F$  (10 $^6~\Omega$  / (0.1 jw + 1) where  $w=2\pi$  freq.). The maximum frequency derived from the CO/PLL/CG block and passing through the LIC is 49.152

MHz (independent of the IEEE-1394 transmission rate). Although at such transmission rate, the measured signal characteristics were quite satisfactory providing a full working unit, we are aware that more studies need to be conducted to select the most appropriate connector and pinout configuration for the PHY-LLC link. As an example, two additional terminals dedicated to data transfer would be required to support the 400 Mb/s transmission rate on the IEEE-1394 cable. Furthermore, three additional connections could be assigned for the power class indicators and one more for power down feature instead of the actual jumper settings on the FWM.

### V. INSTALLATION

The outlet is targeted for the cable environment as described in the IEEE Std. 1394-1995. As such, any physical topologies can be created provided that the resulting network is non-cyclic (no closed loops) with finite branches and extent. The FWM is a module and a node as defined in the IEEE Std. 1394-1995. A module is defined as a physical packaging concept and a node as a logical entity with a unique address. Each module consists of one or more nodes. In the present implementation, each module has only one node. When nothing is connected to the LIC, the module is the outlet itself. When another circuit with a LLC is connected to the LIC, then the new circuit and the FWM combined becomes one module independently of the architecture, units or logical entities (as defined in the IEEE Std. 1394-1995), and functionality of the new circuit. This new module built from an outlet will be designated here as an extended module. An extended module has one node or single address supported by the outlet. We will refer as a functional module a module where both the PHY and the LLC are embedded together and cannot be separated. This is the case of typical IEEE-1394 commercial products.

Although the number of nodes can be expanded through several bridges, up to 63 nodes can be installed per serial bus. Since the outlet is a node, then up to 63 outlets can be interconnected per serial bus. Although implementing an extended module will have no impact on the maximum number of outlets, each functional module will implement an additional node and therefore, reduce the maximum number of outlets that can be installed. This is the price to pay for increase flexibility. Hence, the maximum number of outlets will depend on the number of ports among the outlets available to connect the functional modules.

An outlet can either be a branch (more than one connected ports), or a leaf (only one connection) as defined in the IEEE Std. 1394-1995 where the number of connections or IEEE-1394 ports initially used for networking will vary among outlets. A leaf outlet (one at the end of a branch) can connect two additional functional modules. When doing so, the outlet becomes a branch. Because interconnections between outlets are somewhat permanent, whereas functional modules' connections are not, we use the term leaf and branch outlets assuming that no functional modules are initially plugged to the serial bus. Therefore, each leaf outlet will reduce by two the maximum number of outlets per serial bus. If we define outlets with two or three initial IEEE-1394 connections as

branch-2/3 (2 ports out of 3 used for networking) and branch-3/3 outlets, than each branch-2/3 outlet will reduce the maximum number of outlets by one. The branch-3/3 outlet will have no impact on the maximum number of outlets but will not provide any connections for the functional modules. In summary, the maximum number of outlets per serial bus is  $N=63-2 \cdot N_{\rm LEAF} - N_{\rm BRANH2/3}$  where  $N_{\rm LEAF}$  and  $N_{\rm BRANH2/3}$  are the number of leaf and branch-2/3 outlets in the same serial bus. The cable medium also limits the number of physical connections or cable hops (length of 4.5 meters each) to 16, giving a total cable distance of 72 meters between any two devices. Hence, we know that in a configuration with a maximum number of outlets, at least 4 will be leaf, already reducing the number of outlets by at least 8 unless the number of available ports per leaf outlet is reduced.

As shown, installing an IEEE-1394 based network will have an impact on the number of IEEE-1394 ports available for the user. Improving the availability of the number of such connectors will have an impact on the number of outlets that can be interconnected, making the installation more difficult. Therefore, the installation and interconnection between the outlets is a trade-off between accessibility among distant sites and number of IEEE-1394 ports available to the user. More importantly, reducing the number of IEEE-1394 ports available will restrict the added networked functionality provided by the functional modules.

With the present version of the outlet, maximum functionality independent on the above factors can be maintained with our concept of expansion modules. Since connecting a LLC-based circuit to the LIC will maintain unchanged the number of nodes in the network, up to N expansion modules per serial bus can be added to the number of possible functional modules. The only drawback is that unlike functional modules that can be installed up to 4.5 meters from an outlet, the expansion module must be tightly connected with short terminals to the respective outlet.

## VI. SUMMARY

The implementation of an outlet intended to connect any IEEE-1394 devices to a home/health care network has been briefly described. This fully functional unit can be used as a reference for future versions.

#### REFERENCES

- [1] IEEE Std 1394-1995, IEEE, 372 pages, 1996.

- [2] "TSB21LV03 IEEE 1394-1995 triple-cable transceiver/arbiter," *Data Sheets*, Texas Instruments Inc., 23 pages, 1996.

- [3] R. Raybarman and B. Henehan, "Configuring the TI 400 Mbit PHY as a 1394 Repeater Node," Application Brief SLLA016A, Texas Instruments Inc., 15 pages, 1998.

- [4] B. Henehan, D. Yaklin, B. Gugel, and J. Akgul, "Galvanic Isolation of the IEEE 1394-1995 Serial Bus," Application Report SLLA011, Texas Instruments Inc., 30 pages, 1997.

[5] R. Raybarman and B. Henehan, "PHY Layout," Application Report SLLA020, Texas Instruments Inc., 17 pages, 1997.